PROJECT

Graphics Card

| Akanksh K | AUTHOR | ACTIVE |

| Sudeep Hegde | COORDINATOR | ACTIVE |

Background

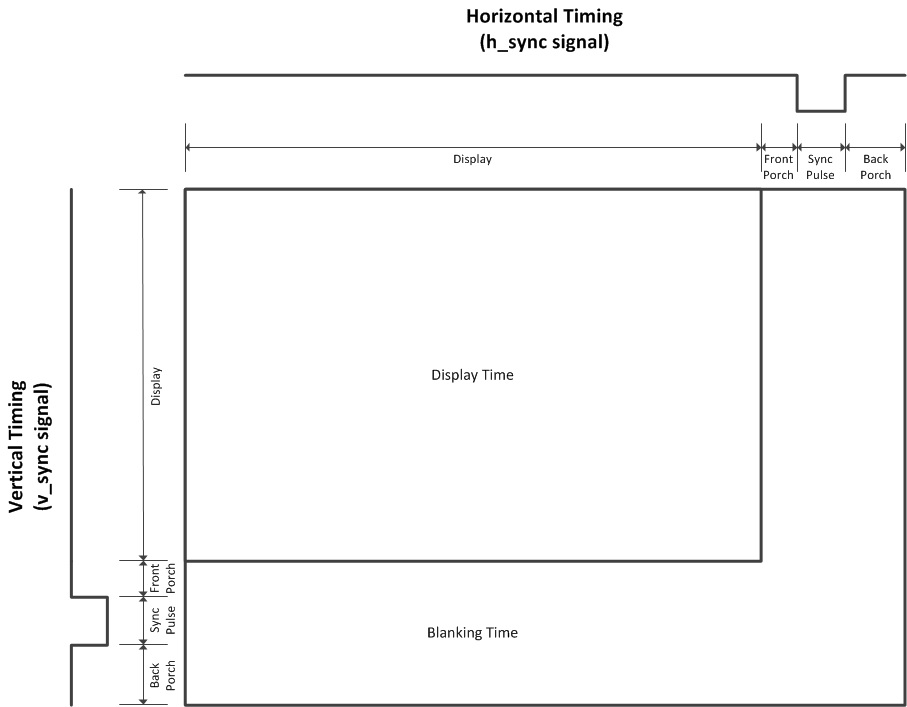

This video card is based on the functions of older CRT displays. While new monitors differ in size, they still follow corresponding timing specifications. Modern monitors rely on horizontal sync (HSYNC) and vertical sync (VSYNC) signals to manage the timing of video data. These signals define the screen's refresh process and control when the image data is sent to the monitor, ensuring the correct display of images. Our design illustrates how pictures can be displayed by leveraging concepts behind counters, logic gate sequences, and control timings to produce a correct VGA output. The VGA standards, although somewhat outdated for newer digital monitors, provide the foundational principles for generating these sync signals and are adapted to different resolutions and display characteristics.

Objective

The challenge is to implement VGA timing signals, specifically the horizontal and vertical sync signals, with accurate timing for the visible area, porches, and sync pulses. Additionally, the project aims to simplify the hardware requirements by using a 10 MHz crystal oscillator to generate a pixel clock, with potential scaling for more manageable timing. The goal is to design a functional video card that can generate VGA signals and display simple patterns.

Implementation

VGA Timing Basics

Understanding the VGA timing standards led to the identification of the essential parts:

- Visible Area: Active display region.

- Front Porch: Blank time after each scan line.

- Sync Pulse: Signal to transition to the next line or frame (e.g., once the horizontal line is filled, a signal is sent to move to the next vertical line).

- Back Porch: Blank time before the next line/frame.

Horizontal Counter Design (HSYNC)

HSYNC (Horizontal Synchronization) is a signal used to indicate the beginning of a new horizontal line in the video display. It ensures that the monitor's electron beam (or pixel rendering process in modern displays) resets at the end of each line and starts drawing the next one.

In our case, we are using a 10 MHz crystal oscillator to generate the timing signals, whereas the standard pixel clock for VGA is typically 40 MHz. Therefore, we must scale down the VGA timings to accommodate the lower clock frequency.

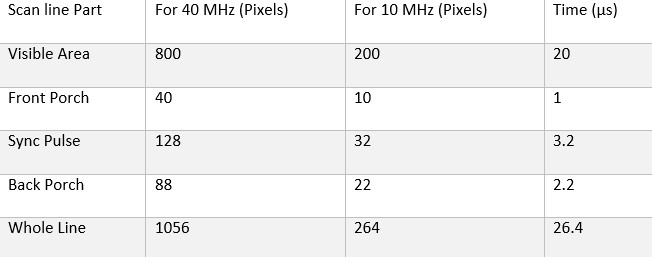

VGA Timing Calibration for 10 MHz

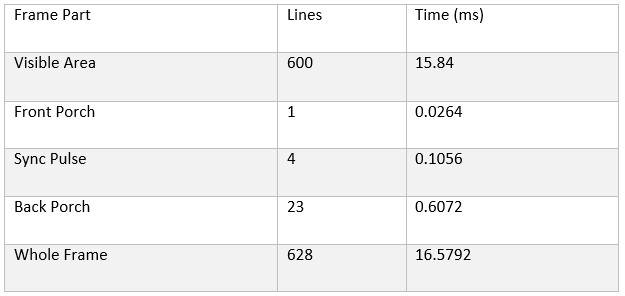

To achieve correct timing at a 10 MHz clock, we proportionally scale down the standard VGA timings from 40 MHz. The following table summarizes the scanline components and their respective pixel counts and timings:

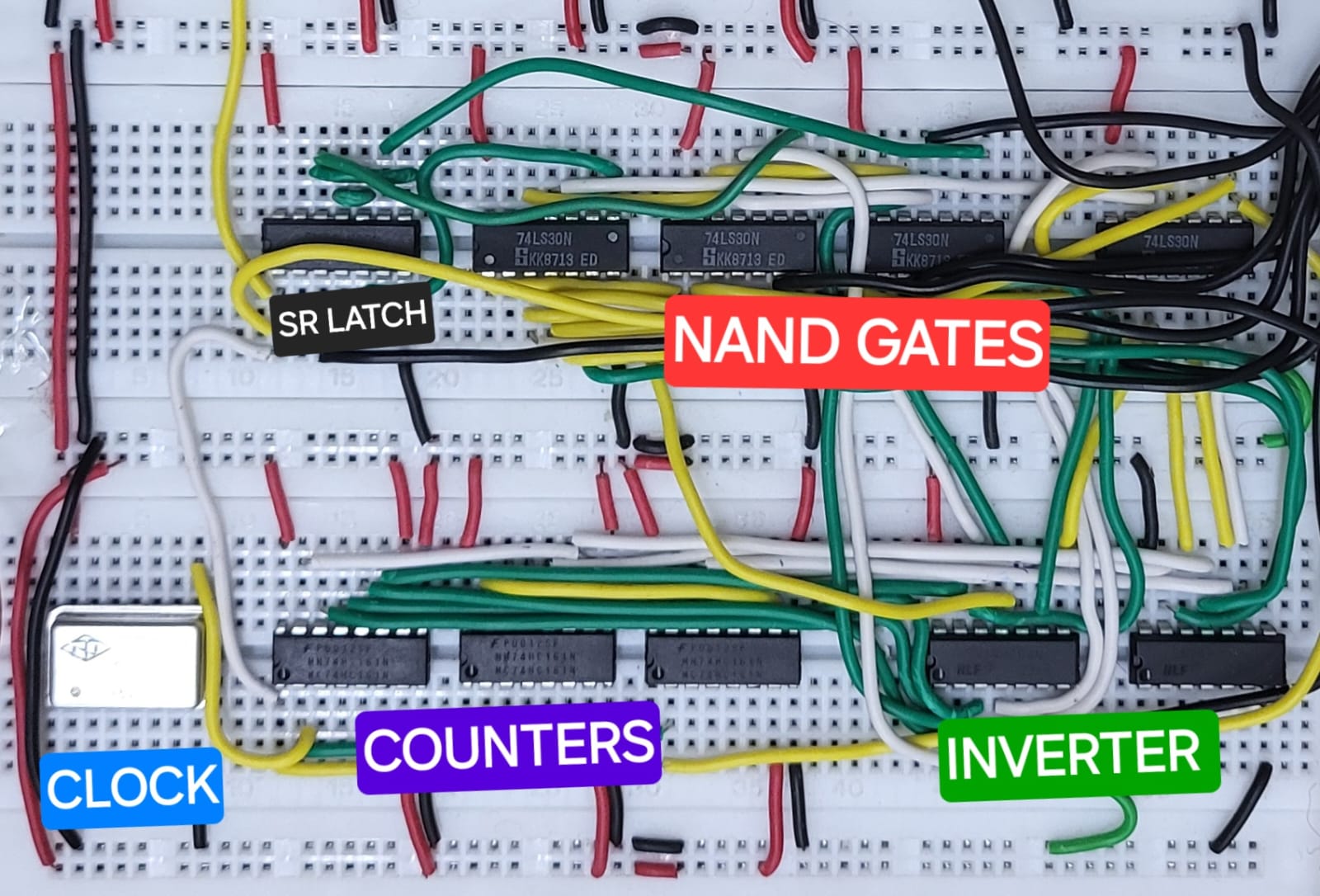

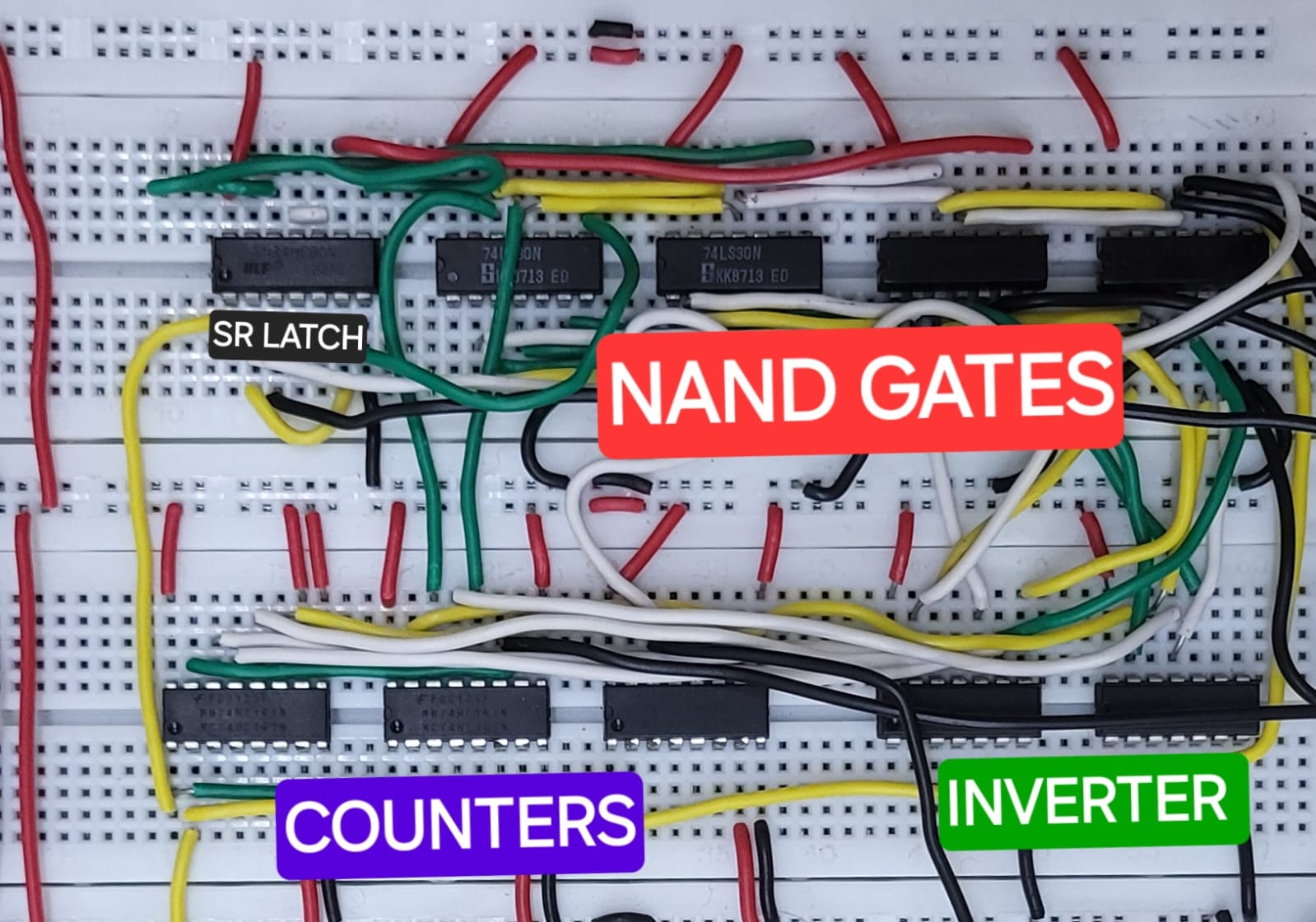

To implement this, we use a set of three 74LS161 4-bit counters configured to work as a 9-bit counter. The timing mechanism is controlled by a 10 MHz oscillator, with the counters resetting after reaching a value of 264 to maintain the scan line timing.

Implementation Details

- Counter Setup: The counters are cascaded with ripple-carry outputs, which are enabled to pass the count to subsequent counters.

- Reset Mechanism: The counters reset when they reach a count of 264, ensuring the start of a new scan line after completing the current one.

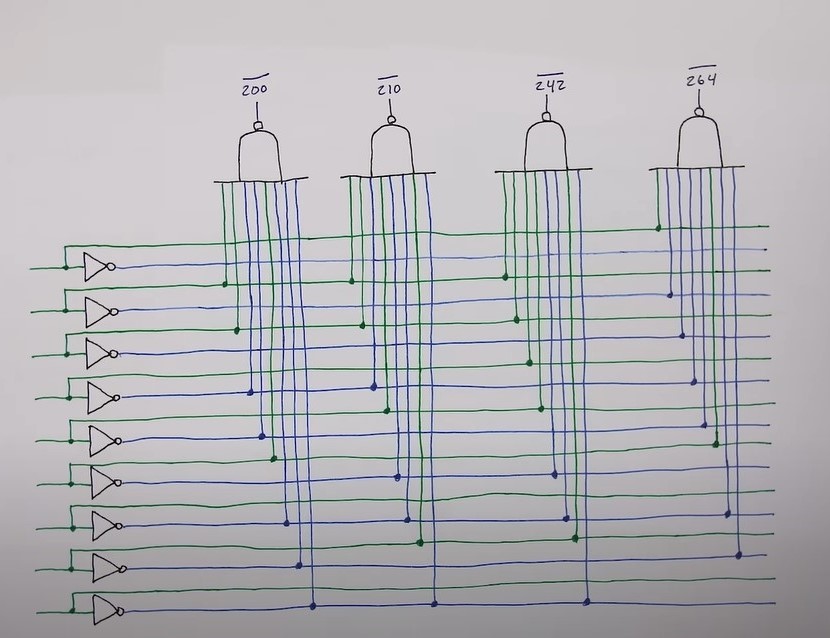

To map the pixel counts from the timing table, we convert the relevant values into binary:

- 200: 011001000 (Visible area)

- 210: 011010010 (Front porch)

- 242: 011110010 (Sync pulse)

- 264: 100001000 (Back porch)

Signal Generation with NAND Gates

To generate the appropriate signals for each section (Visible area, Front porch, Sync pulse, and Back porch), we use 74LS30 8-input NAND gates. These gates combine the inverted and non-inverted outputs from the counters corresponding to the mapped binary values.As we are using 8 input nand gate but the output is having 9 inputs hence the MSB in 200,210,242 is zero which can be ignored similarly the LSB of 264 is 0 which can be ignored

The process involves using SR latches or flip-flops controlled by the NAND gates to set and reset signals as follows:

- The latch is set when the counter enters a section (e.g., Visible Area) and reset when the counter exits the section (e.g., at the end of the Front Porch or Sync Pulse).

- For the Sync Pulse, the latch is set at count 208 and reset at count 240.

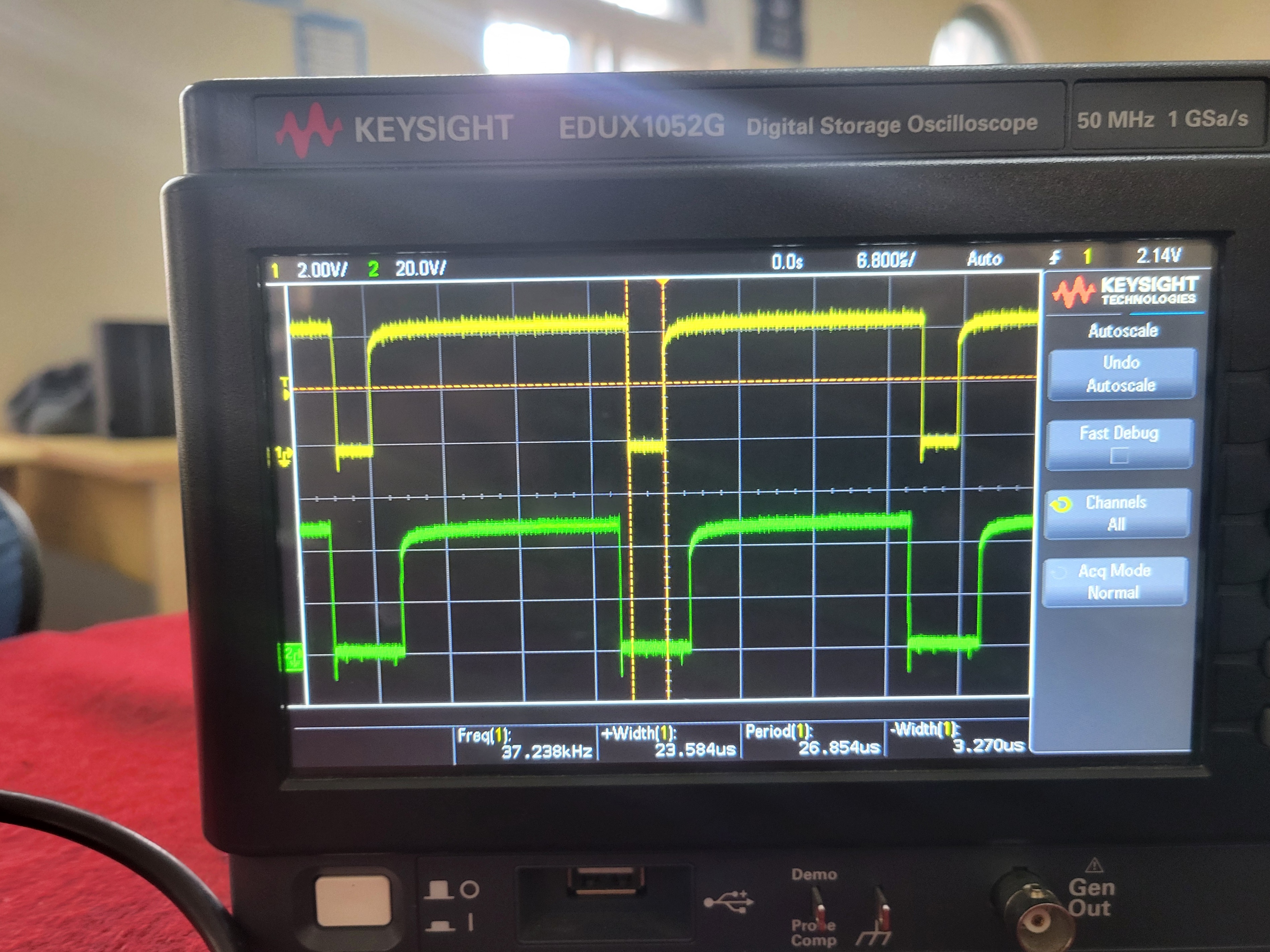

Finally, we verify the timing using an oscilloscope, ensuring the total horizontal period equals 26.4 µs. This confirms the synchronization of the horizontal scanline according to the desired timing.

Finally, we verify the timing using an oscilloscope, ensuring the total horizontal period equals 26.4 µs. This confirms the synchronization of the horizontal scanline according to the desired timing.

Vertical Counter Design (VSYNC)

VSYNC (Vertical Synchronization) ensures the proper timing for the start of a new frame by resetting the vertical scanline counter at the end of each frame. Similar to the horizontal counter, the vertical counter divides the frame into distinct sections based on the VGA timing standard.

In our implementation, the vertical counter works in tandem with the horizontal counter and is updated once the horizontal counter completes a full scanline. Using a 10 MHz clock, we proportionally scale down the standard VGA timings for the vertical frame.

VGA Timing Calibration for 10 MHz (Vertical)

The following table outlines the vertical timing details for a frame:

Implementation Details

Counter Setup:

- A vertical counter increments every time the horizontal counter completes a full scanline (i.e., resets).

- The vertical counter resets after reaching a count of 628, which marks the completion of a frame.

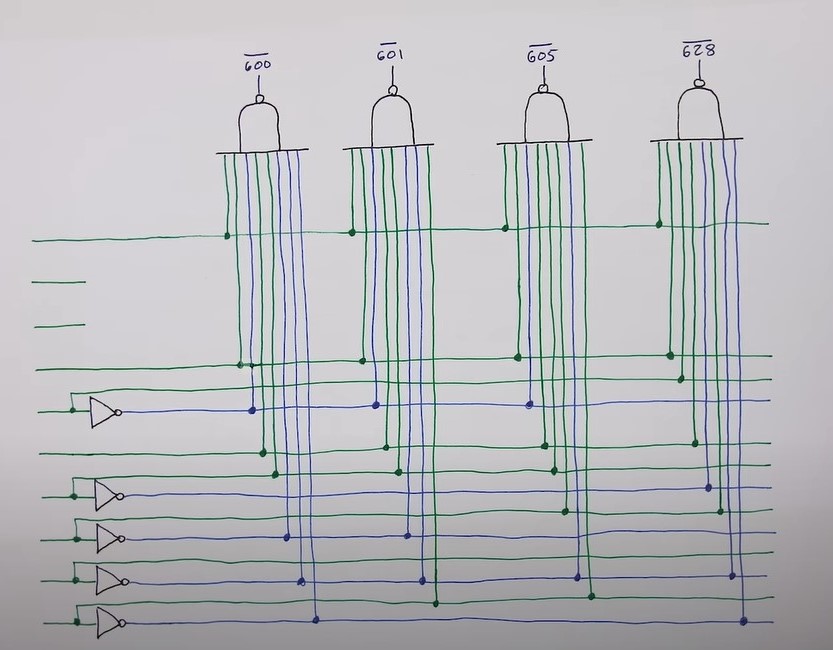

Mapping Vertical Timings to Binary:

- 600: 1001011000 (End of Visible Area)

- 601: 1001011001 (Start of Front Porch)

- 605: 1001011101 (End of Sync Pulse)

- 628: 1001110100 (Frame Reset)

Signal Generation with NAND Gates:

To generate VSYNC signals and section intervals, 74LS30 8-input NAND gates are used, combining the inverted and non-inverted outputs of the vertical counter corresponding to these binary values. As we are using 8 input nand gates but we need 10 inputs here, So we can see that the 2 bits after the MSB is zero always hence we can ignore them.

Latch Mechanism for VSYNC Pulse:

- SR latches or flip-flops, controlled by the NAND gates, are used to define and control the intervals of each section.

- For the Sync Pulse, the latch is set at line 601 and reset at line 605.

Integration with HSYNC:

- The vertical counter integrates seamlessly with the horizontal counter to produce synchronized VSYNC and HSYNC signals, ensuring correct timing for frame transitions.

Verification:

- The complete vertical timing is verified using an oscilloscope to ensure the frame duration matches 16.7 ms, as required by the VGA standard.

By combining the vertical and horizontal counters, a synchronized VGA signal is generated, meeting the timing specifications for 10 MHz operation.

Combining HSYNC and VSYNC

To generate valid VGA signals, the horizontal (HSYNC) and vertical (VSYNC) synchronization signals must be combined and properly timed. These signals ensure that the display is refreshed correctly for both individual lines and entire frames.

Synchronization Signal Integration

- HSYNC: Active during the horizontal sync pulse interval, connected to Pin 13 of the VGA connector.

- VSYNC: Active during the vertical sync pulse interval, connected to Pin 14 of the VGA connector.

- Both signals are measured using an oscilloscope to confirm correct frequencies:

- HSYNC Frequency: 37.8 kHz

- VSYNC Frequency: 60 Hz

Pixel Data Enable

- The pixel data is sent only during active periods of both horizontal and vertical intervals.

- Achieved by ANDing the active time slots of HSYNC and VSYNC, ensuring pixel data is transmitted only when the display is ready to receive it.

Generation of RGB Signals

To display colors on a VGA monitor, three primary color signals—Red, Green, and Blue (RGB)—are generated. These signals are then scaled to meet the VGA voltage specifications using a resistor network.

RGB Signal and Voltage Divider Setup

RGB Signal Generation:

- The three color signals (Red, Green, Blue) determine the pixel color displayed on the monitor.

- Binary counter outputs or data from EEPROM control the RGB values to create patterns or images.

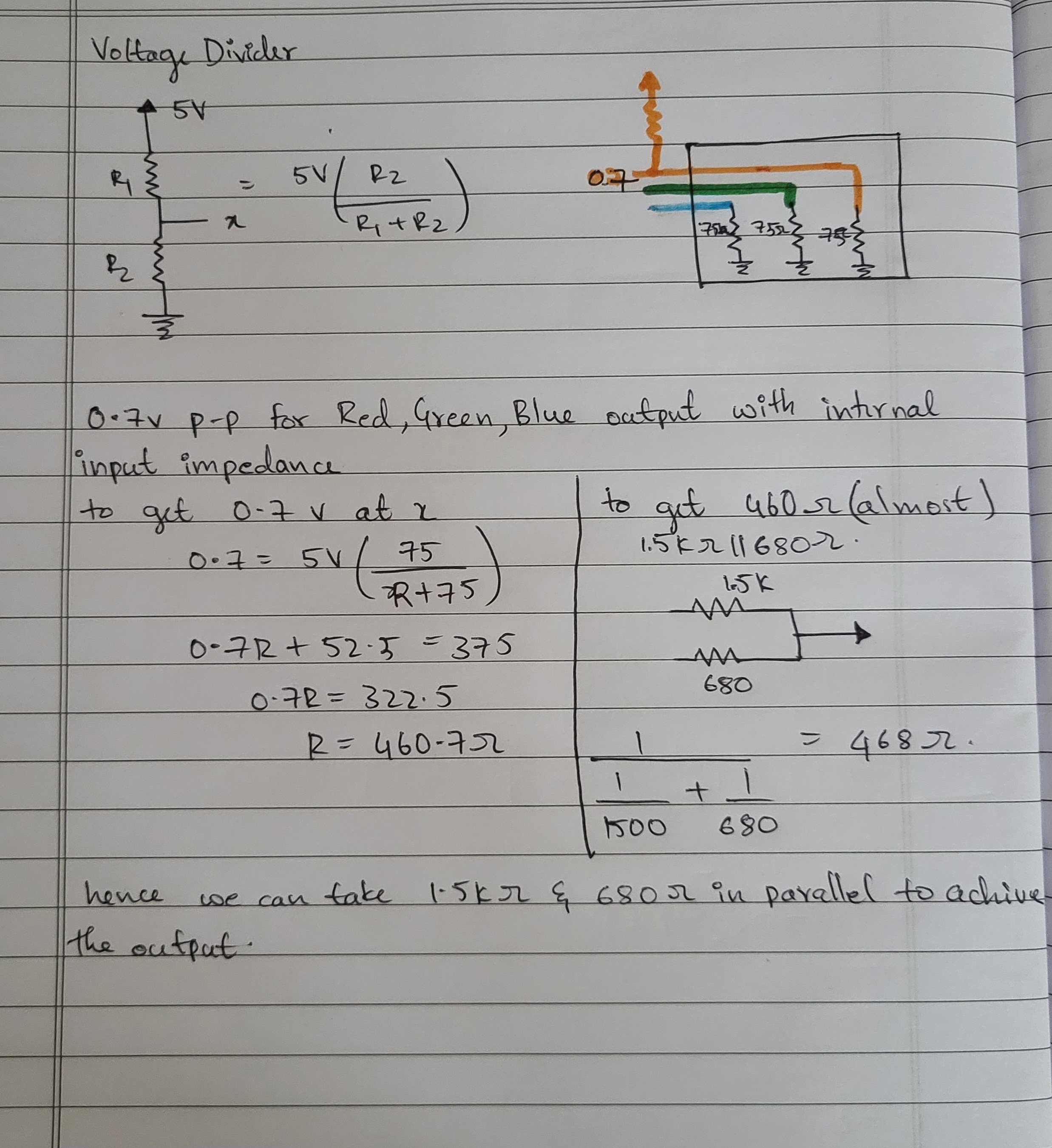

Voltage Divider for VGA Specifications:

- VGA color pins require voltage levels between 0 V and 0.7 V to produce varying pixel intensities.

- A resistor network functions as a voltage divider to scale the digital signals into the required analog voltage levels.

Resistor Network Design:

- To achieve proportional intensity scaling:

- Higher Bit: Resistor value of 680 Ω for higher intensity.

- Lower Bit: Resistor value of 1.5 kΩ for lower intensity.

- The monitor’s 75 Ω impedance ensures proper current scaling to produce the expected color output.

Scaling with Resistors:

- The VGA's 75 Ω impedance forms part of the voltage divider circuit.

- Additional resistors are added to scale the signals properly:

- 460.7 Ω resistors ensure correct voltage levels for RGB signals.

- Signals from counters/EEPROM (digital) are converted to analog voltages using this setup.

Voltage Mapping for Pixel Intensity:

The resistor network maps digital binary inputs to analog voltage levels for varying intensities:

- 00: 0 V (Off)

- 01: ~0.23 V

- 10: ~0.47 V

- 11: ~0.7 V (Full Brightness)

This resistor-based voltage divider system enables precise analog voltage generation for each RGB channel, allowing the monitor to interpret digital pixel data accurately.

Pin Connections:

- Sync Signals: HSYNC to Pin 13, VSYNC to Pin 14

- RGB Signals: Red: Pin 1, Green: Pin 2, Blue: Pin 3

- Ground Pins: Pins 5, 6, 7, 8, and 10

Once connected, the VGA monitor recognizes a valid signal for 800×600 @ 60 Hz resolution.

Testing Patterns and Gradients

By connecting the generated signals to specific parts of the horizontal and vertical synchronization circuits, test patterns (e.g., gradients) can be displayed.

Memory Integration for Pixel Data

To display complex patterns or images, pixel data is stored in external memory and retrieved during display intervals.

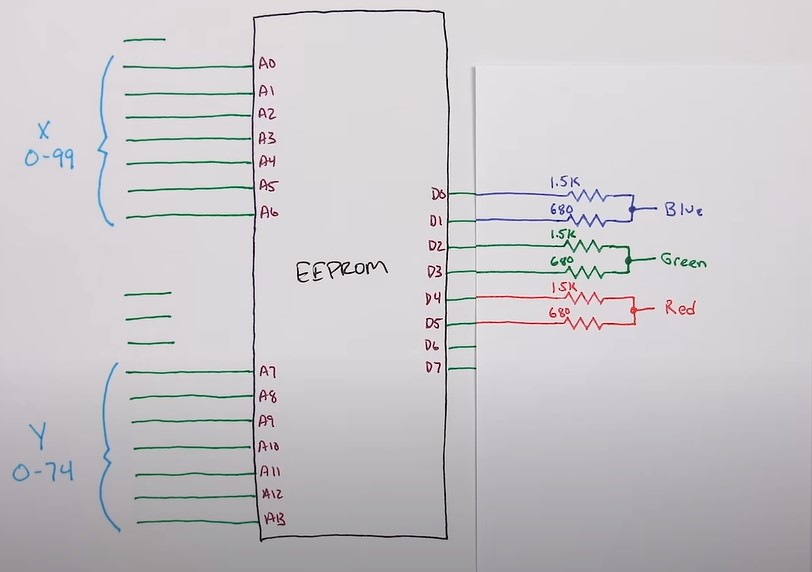

Memory Selection and Integration for Pixel Data

Memory Specifications:

- The 28C256 EEPROM has a storage capacity of 32 KB, enabling pixel data storage for small resolutions.

- The address range is configured to 256 × 256, which is adjusted based on the desired resolution.

Resolution Constraints:

- Due to limitations in address lines, the resolution is scaled down to 100 × 75 pixels.

- Horizontal (7 bits) and vertical (7 bits) counters are used to address the EEPROM.

Pixel Addressing Mechanism:

- Each pixel's position is mapped directly to an EEPROM address using the formula:

Address=(Vertical[6:0]≪7)∣Horizontal[6:0]. - Only the 7 least significant bits from both counters are used due to resolution constraints.

Aspect Ratio Maintenance:

- To preserve the aspect ratio, pixels are stretched horizontally and vertically for display on the VGA monitor.

Pixel Data Retrieval

Visible Interval Data Loading:

- During visible intervals, pixel data is dynamically retrieved from EEPROM and output through the RGB resistor network to the VGA connector.

Blanking Interval Handling:

- Initial testing revealed a blank screen caused by improper handling of blanking intervals.

- A NAND gate was introduced to detect blanking intervals and control the EEPROM's output enable (OE) pin, ensuring proper timing and synchronization.

Signal Correction:

- Wiring corrections were made by swapping the NAND gate outputs to generate inverted signals, resolving the blanking interval issue.

Image Processing and EEPROM Programming

To display a colorful image on the VGA monitor, the image data was carefully prepared, processed, and programmed into the EEPROM. This section outlines the steps involved in preparing the image, generating raw pixel data, programming the EEPROM, and future improvements to enhance the system. Data is organized to match the 100 × 75 pixel resolution, ensuring compatibility with the counter-driven addressing system.

Preparing the Image

Image Selection and Resizing:

- A colorful image was selected and resized to match the scaled-down resolution of 100 × 75 pixels.

Color Indexing:

- The image was indexed to a custom 64-color palette, designed to match the output levels of the resistor voltage divider network for VGA color signals.

Creating Raw Pixel Data

Pixel Data Conversion:

- Python and the Python Imaging Library (PIL) were used to process the image and create a binary file (image.bin) containing raw pixel data.

Hexadecimal Conversion:

- The binary pixel data was converted into a hexadecimal format using a custom Python script, making it compatible with the EEPROM programming process.

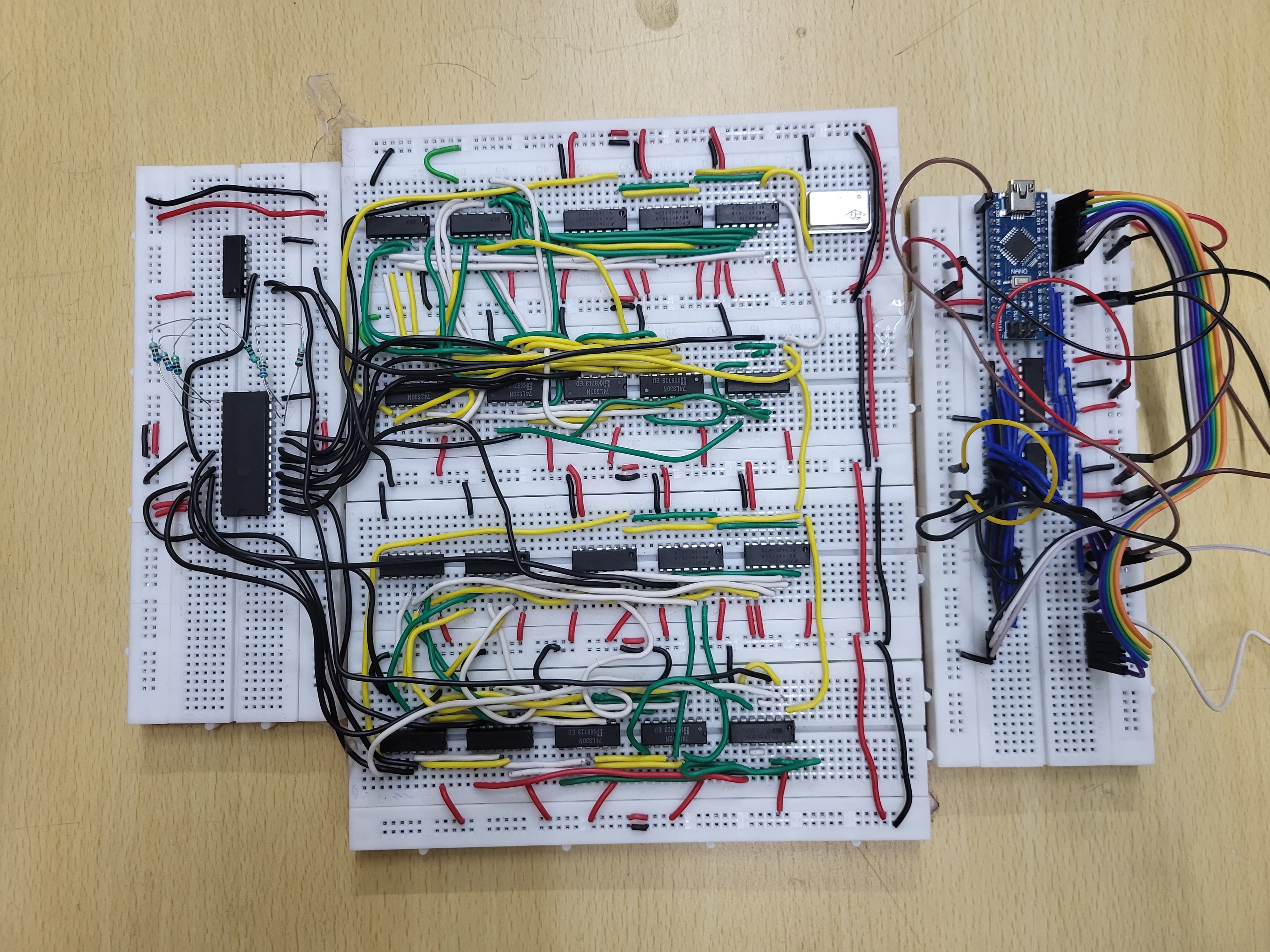

Programming the EEPROM

Hardware Setup:

- An Arduino Nano and shift registers were used to create a custom EEPROM programmer capable of writing the pixel data into the AT28C256 EEPROM.

Programming Process:

- The processed hex file containing the image data was loaded into the EEPROM using the custom programmer. The memory layout aligned with the pixel addressing mechanism designed in the circuit.

The program links are given here https://github.com/Akanksh003/Graphics-Card

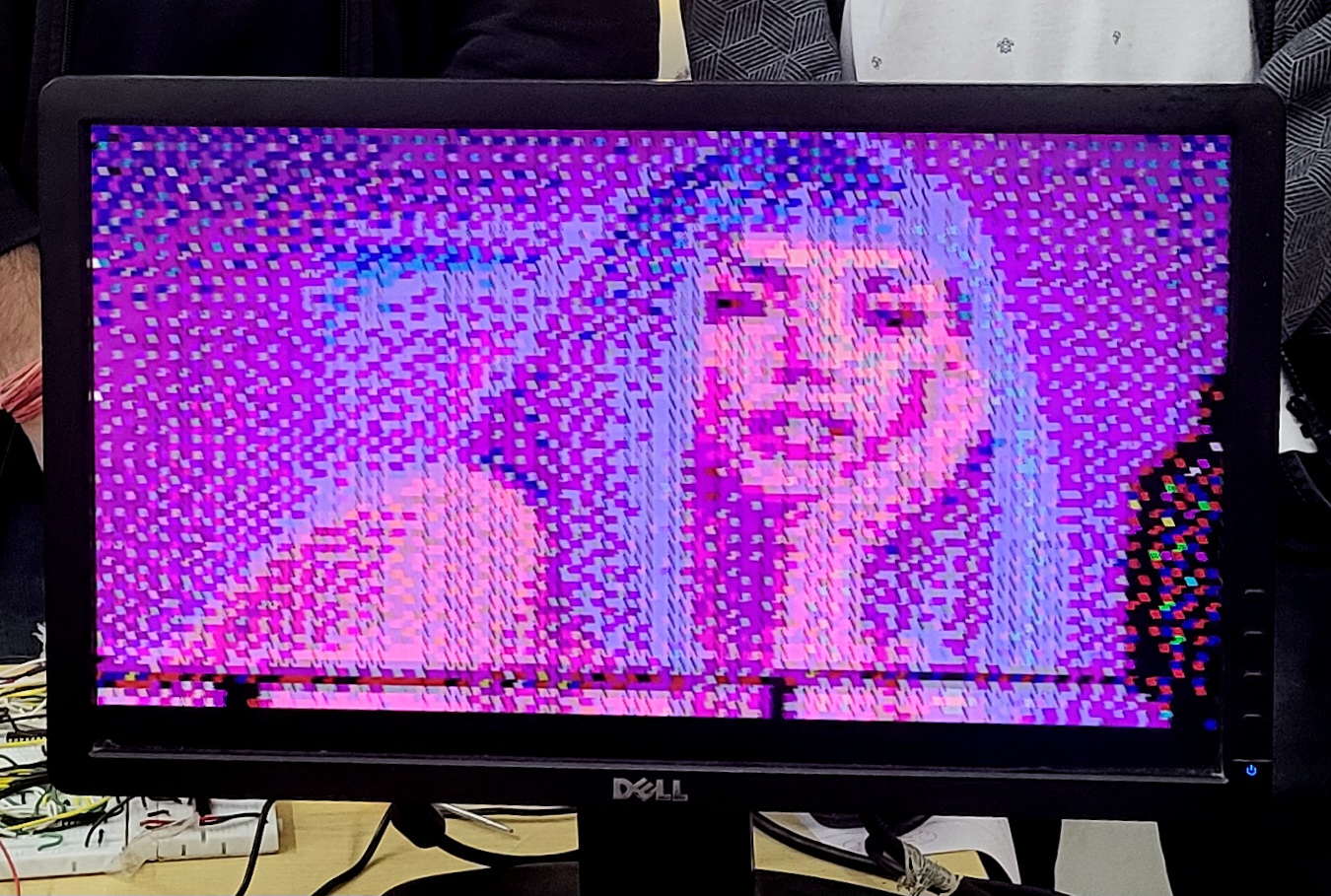

Final Results

- The system successfully displayed the test image on the VGA monitor with accurate colors and proper alignment.

- Reference links - https://eater.net/vga

- I would like to thank Ben Eater for the idea to make this project to come true